Quartus II 实验 (三)——图形化编程4位全加器,4位乘法阵列

本文共 579 字,大约阅读时间需要 1 分钟。

0x1前言

计算机组成原理实验项目之一,要求使用Quartus II 的图形化编程制作 4位全加器 和 两个4位四位数相乘的乘法阵列。

本篇假定,你已经掌握Quartus II 和 DICE-E213实验箱的基本使用,如果遇到问题可以参考

x02制作 4位全加器

步骤一:制作一个半加器

导出半加器,并作为模块存放到下一个工程的目录下,具体做法可以参考,以后的每个工程的调用以此类推。需要注意,调用很可能是递归的,所以所有引用的模块都要连带传递。

步骤二:制作一个全加器

步骤三:制作一个4位加法器

步骤四:排布引脚

- 引脚对应图:

步骤五:编译,上电!烧入实验箱

步骤七:测试

测试时看准引脚对应的输入,并且需要强调对于本试验箱输出模块亮为0灭为1,找到那一端是地位那一端是高位,比较无脑,不再赘述。

0x3制作 4位乘法阵列

- 流程和上面一样,这里不再赘述,贴一下引脚图做一点说明:

ABCD是初始置0000,开关输入量一定要置0000,否则结果不对,CC是低位进位。

另外是,两组4位输入,和一组8位输出。

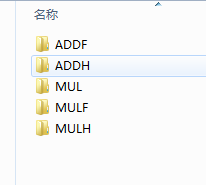

- 目录结构是:

ADDH-->ADDF-->MULH-->MULF-->MUL

0x4提供以上两个工程的源文件,供大家参考。

四位乘法阵、\四位加法器 公共下载区

备用链接:

0x5结束收工

在试验过程中如有错误,欢迎留言,讨论,也欢迎指出我的错误。

转载地址:http://cnoen.baihongyu.com/

你可能感兴趣的文章

oracle10g rac 报ora-12545错误的解决方案 转载

查看>>

Linux配置Xmanager

查看>>

IP地址正则表达式

查看>>

对SOAP消息头的处理

查看>>

webservice TCP Monitor

查看>>

Oracle中sysdate的时区偏差

查看>>

【每日一算】旋转有序数组

查看>>

【每日一算】两数之和

查看>>

深入理解Mysql索引底层数据结构与算法

查看>>

B+树算法在mysql中能存多少行数据?

查看>>

【vue学习】—条件判断、循环遍历

查看>>

【vue学习】—slot插槽的使用

查看>>

怎样做研究

查看>>

调试串口通用程序的几种技巧

查看>>

GUI 编辑框中读写矩阵

查看>>

matlab成段注释

查看>>

福听阅读器 背景色设置

查看>>

华硕 P5KPL-AM 前面板耳机没有声音

查看>>

labview 局部变量问题

查看>>

labview 循环外部与数组相连时问题

查看>>